The Economics of Late Discovery

Inspection Coverage as Risk Containment

Failure Analysis as a Decision Accelerator

Conclusion: Inspection and Failure Analysis as Strategic Levers in Semiconductor Fabs

References and Further Reading

From the 1994 Pentium FDIV bug, which cost Intel an estimated $475 million, to the RowHammer DRAM vulnerability exposed in 2014, the history of industry shows that when defect detection and failure analysis (FA) fail to keep pace with process complexity, the consequences can extend far beyond engineering teams.1,2

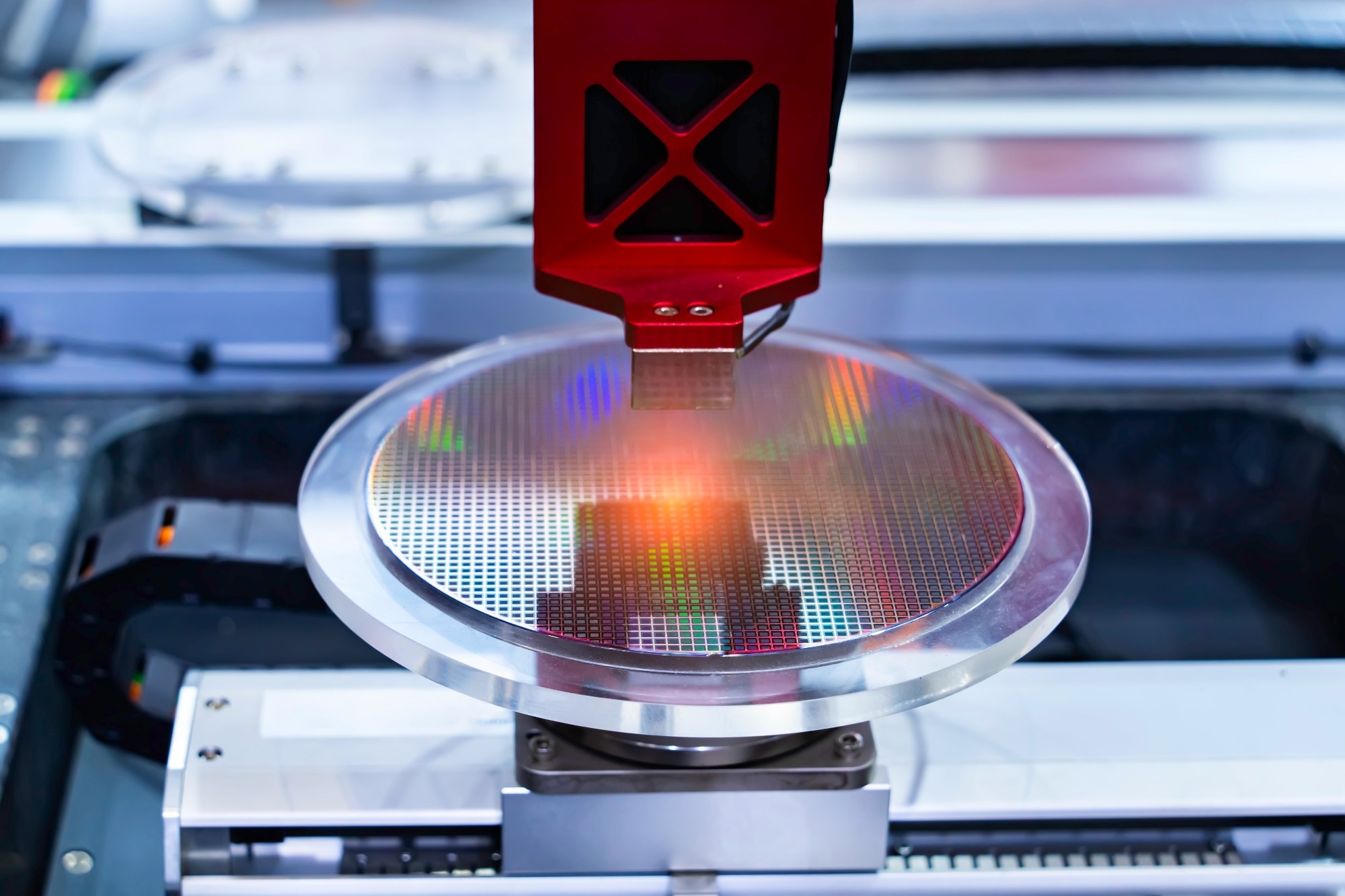

Image Credit: asharkyu/Shutterstock.com

In advanced semiconductor manufacturing, even small defects can propagate across high-value wafers, enter high-volume supply chains, and surface months later as reliability failures or security vulnerabilities.

The underlying issue is often perceptual. Inspection is frequently categorized as overhead, and FA as a reactive support function. Yet both determine how quickly uncertainty is identified, the confidence companies can ascribe to corrective action, and the level of risk that accumulates before a problem is contained. In a capital-intensive environment where margins depend on yield ramp speed and delivery predictability, uncertainty represents a significant liability.

To understand why inspection and FA should be treated as strategic investments rather than cost centers, it is necessary to examine the economics of when defects are discovered, and how quickly they are resolved.

Save this PDF for later by downloading it here.

The Economics of Late Discovery

In semiconductor manufacturing, the financial impact of a defect depends less on its physical size than on the time it is discovered. If identified early, it may require only a localized engineering adjustment and limited scrap. If it escapes into later production stages, the cost multiplies, not only because more material and processing time have been invested, but because profitability in semiconductor ventures depends heavily on how quickly yield improves and volume ramps occur.3

Delays in yield learning (the structured process by which a fab improves wafer yield by eliminating the causes of defects and variability) erode cumulative profit, while early acceleration more than doubles it. Late defect discovery therefore does not merely increase scrap; it delays yield ramp, extends cycle time, increases work-in-process inventory, and compresses the market window in which profits can be earned.4

When defects escape even further, such as into the shipped product, the escalation becomes more severe. Industry analysis notes that a latent defect reaching the market can trigger repair costs, refunds, recalls, and liabilities that may be 10 to 100 times greater than simple material scrap costs.5

Inspection Coverage as Risk Containment

Inspection coverage, which is reflected in sampling plans across tools, lots, and process steps, determines how quickly a fab can detect emerging problems and how much risk can accumulate before detection.6 Because only a fraction of production can realistically be inspected, coverage decisions effectively define which parts of the manufacturing system are visible and which remain unobserved.

The IRDS Yield Enhancement roadmap frames yield improvement as an ongoing exercise in identifying and mitigating risk across materials, tools, utilities, and environments. Within this context, inspection density becomes a practical mechanism for implementing risk analysis: it determines how much of the system is actively monitored and how rapidly parameter shifts outside specification limits, so-called “excursions”, can be detected.7,8

Sparse inspection creates longer blind periods in which excursions may persist unnoticed. Denser, strategically placed inspection shortens feedback loops, increasing the likelihood that anomalies are detected close to their point of origin, when containment is still feasible, and downstream disruption is limited.

This becomes more critical as scaling advances.

IRDS notes that physical device dimensions and corresponding defect dimensions continue shrinking while overall process complexity increases, placing greater emphasis on defect detection and classification technologies capable of delivering high sensitivity at high throughput to support prompt yield learning and cost-efficient manufacturing. In effect, inspection coverage sets the upper bound on how much systemic manufacturing risk a fab is able, or willing, to carry.8

Failure Analysis as a Decision Accelerator

Detecting a defect is not the same as understanding it. In semiconductor manufacturing, the speed and quality of FA determine how quickly uncertainty can be reduced and operational decisions can resume.

The Learning Cycle (LC) framework described in recent yield ramp-up research explicitly includes defect and failure analysis, experimental summary, and process parameter improvement as critical stages in each iteration of yield acquisition. Each LC can take weeks to months, and shortening this cycle directly improves ramp-up efficiency and time to stable mass production. When LC efficiency was improved through structured defect traceability and yield prediction, ramp-up time was shortened by nearly 17.6 %, demonstrating the economic value of accelerating root-cause resolution.9

The commercial stakes are even higher in high-reliability sectors.

Automotive fabs recognize that when latent defects escape into the field, manufacturers may bear the cost of expensive and time-consuming failure analysis, along with warranty claims, recalls, and legal liabilities. Because the cost of discovery and mitigation increases significantly at each downstream level of the supply chain, there is a strong incentive to resolve root causes rapidly and within the fab.10 In this context, FA functions not merely as diagnostic support, but as a mechanism for compressing uncertainty, stabilizing yield learning, and protecting long-term profitability.

Conclusion: Inspection and Failure Analysis as Strategic Levers in Semiconductor Fabs

Inspection and failure analysis are not ancillary engineering functions; they are instruments of economic control. They determine how quickly uncertainty is reduced, how reliably yield improves, and how much risk reaches the customer.

As technology bounds toward escalating complexity and shrinking margins, fabs that treat defect management as a strategic capability, not a cost center, secure both performance and competitive resilience.

References and Further Reading

- Pratt, V. (1995). Anatomy of the Pentium bug. In: Mosses, P.D., Nielsen, M., Schwartzbach, M.I. (eds) TAPSOFT '95: Theory and Practice of Software Development. Lecture Notes in Computer Science. DOI:10.1007/3-540-59293-8_189, https://link.springer.com/chapter/10.1007/3-540-59293-8_189.

- Mutlu, O., et al. (2019). RowHammer: A Retrospective. arXiv:1904.09724 DOI:10.48550/arXiv.1904.09724, https://arxiv.org/abs/10.48550/arXiv.1904.09724.

- Weber, C. (2004). Yield Learning and the Sources of Profitability in Semiconductor Manufacturing and Process Development. IEEE Transactions on Semiconductor Manufacturing. DOI:10.1109/TSM.2004.835724, https://ieeexplore.ieee.org/document/835724.

- Hauck, Z., et al. (2022). Impact of early inspection on the performance of production systems – insights from an EPQ model. Applied Mathematical Modelling. DOI:10.1016/j.apm.2022.03.003, https://www.sciencedirect.com/science/article/pii/S0307904X22001202.

- Haley, G. (2024). [Online] Hidden Costs and Tradeoffs in IC Quality. Semiconductor Engineering. Available at: https://semiengineering.com/hidden-costs-and-tradeoffs-in-ic-quality/ (Accessed on 15 February 2026).

- McNames, J., et al. (2004). In-line Monitoring Coverage Visualization. In: 2004 IEEE/SEMI Advanced Semiconductor Manufacturing Conference and Workshop. IEEE. DOI:10.1109/ASMC.2004.1309551, https://ieeexplore.ieee.org/document/1309551.

- Munga, J.N., et al. (2011). Optimized management of excursions in semiconductor manufacturing. Proceedings - Winter Simulation Conference. DOI:10.1109/WSC.2011.6147923, https://ieeexplore.ieee.org/document/6147923.

- IEEE. (2024). International Roadmap for Devices and Systems: 2024 Edition. Available at: https://irds.ieee.org/images/files/pdf/2024/2024IRDS_YE.pdf.

- Xu, H-W., et al. (2024). A fast ramp-up framework for wafer yield improvement in semiconductor manufacturing systems. Journal of Manufacturing Systems. DOI:10.1016/j.jmsy.2024.07.001, https://www.sciencedirect.com/science/article/pii/S0278612524001407.

- Price, D.W., et al. (2018). Process Watch: Baseline yield predicts baseline reliability. Solid State Technology. KLA Tencor. Available at: https://www.kla.com/documents/02_ProcessWatchAutomotive_2018_03.pdf.

Disclaimer: The views expressed here are those of the author expressed in their private capacity and do not necessarily represent the views of AZoM.com Limited T/A AZoNetwork the owner and operator of this website. This disclaimer forms part of the Terms and conditions of use of this website.